High-performance computing and data center industry always requires the fastest and most power-efficient computer systems. However, facing the end of single-thread and multi-thread performance scaling, computer architects now suffer from critical challenges to further improve the performance and power efficiency with conventional room-temperature computing.

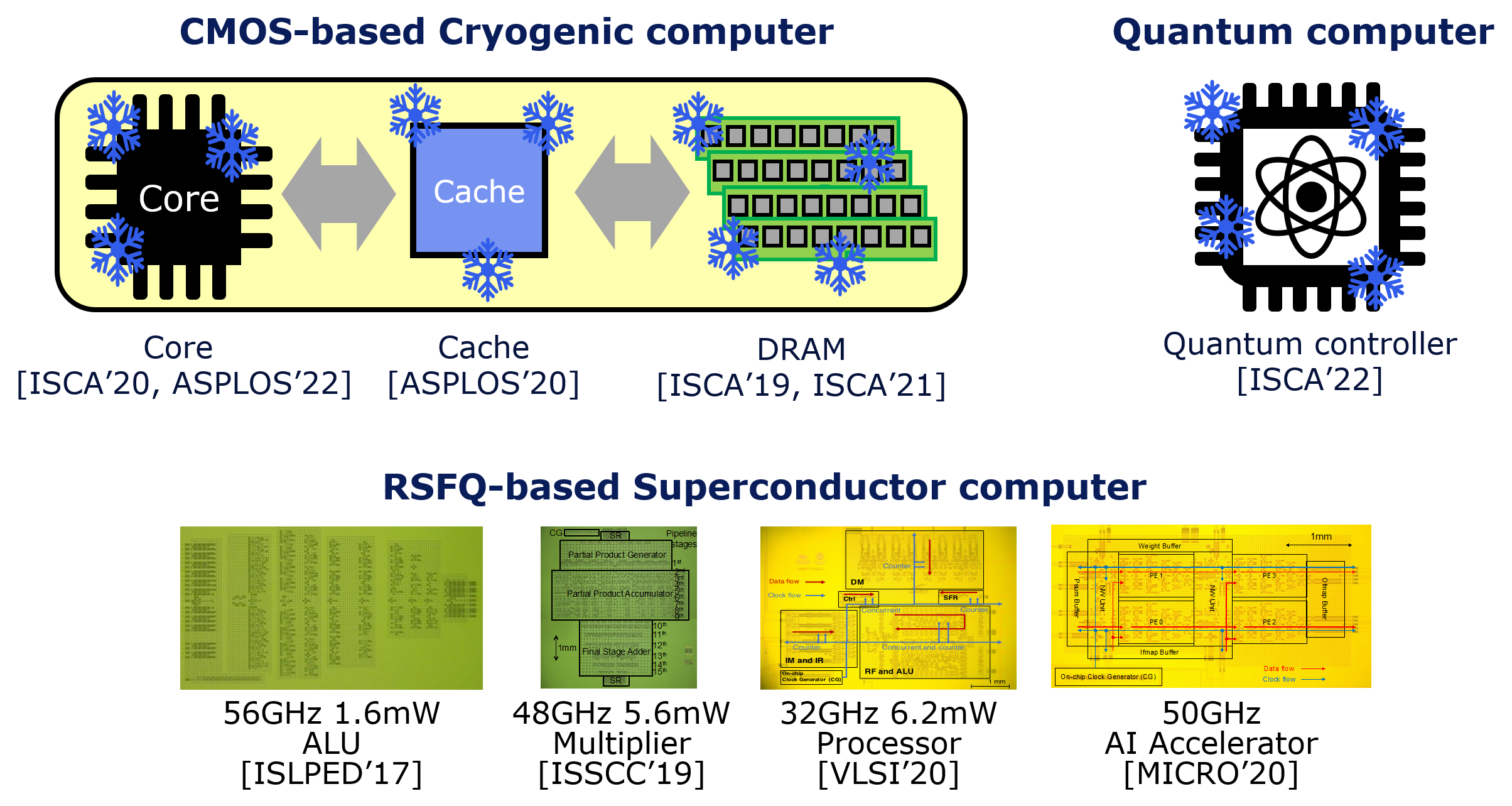

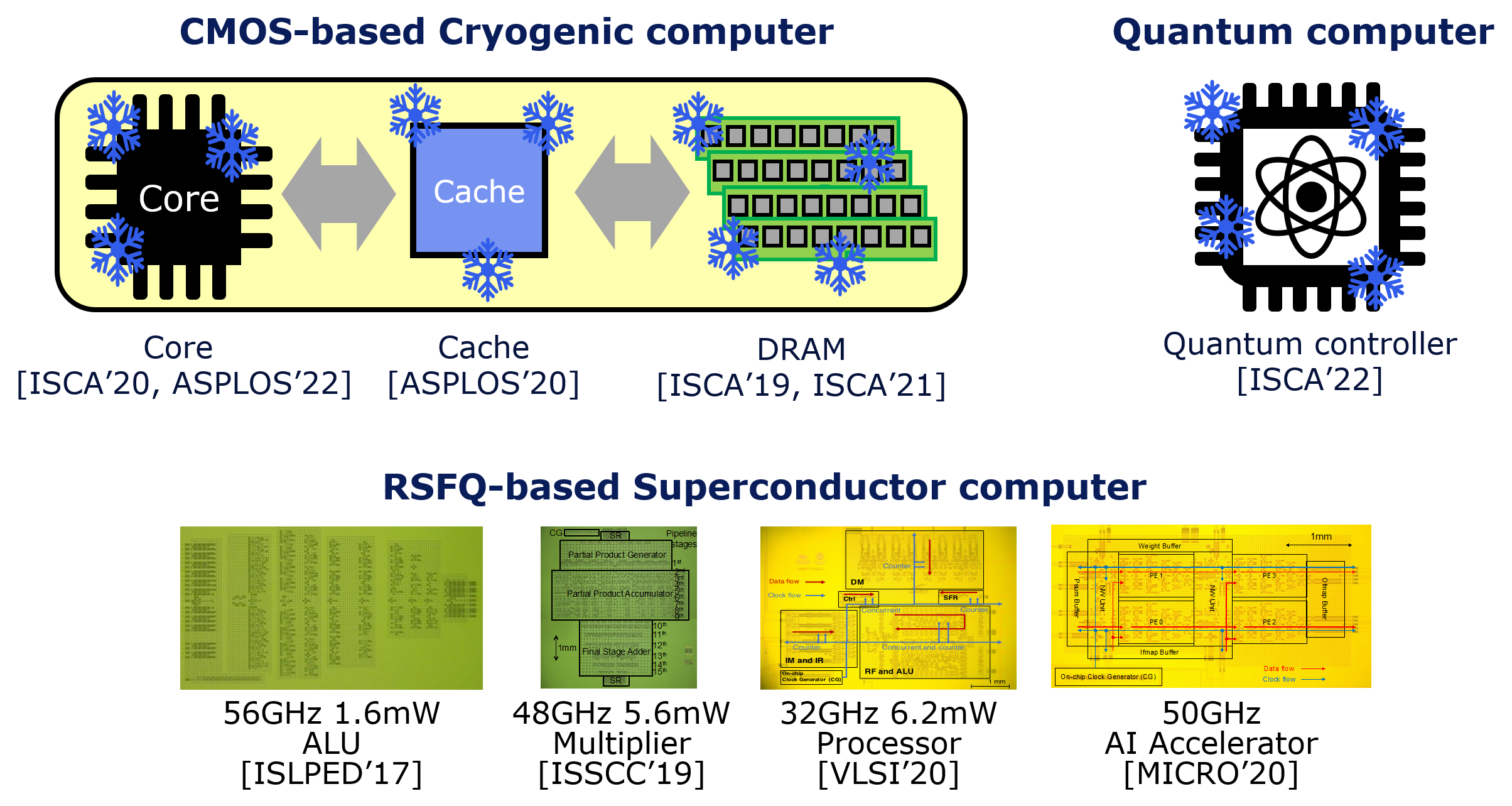

To resolve the problems, researchers at Seoul National University, Kyushu University, and Nagoya University have focused on cryogenic/superconducting computing which architects and operates computers at extremely low temperatures. Our research goal is to maximize the performance of conventional computers (i.e., cryogenic/superconducting computing) and to realize the next-generation innovative computers (e.g., superconducting AI accelerator, scalable quantum computer). Our key achievements can be briefly summarized as (1) 77K CMOS-based cryogenic computing, (2) 4K superconductor-based computing, and (3) mK qubit-based quantum computing.

To realize the research, we developed a series of software tools to model the performance and power consumption of various cryogenic/superconducting computer devices and systems (e.g., 77K core, cache, DRAM, cache, network-on-chip, quantum-control processor).

In this tutorial, we plan to introduce our modeling and design tools which can be used for developing (1) cryogenic CMOS-based computer, (2) superconductor-based computer, and (3) fault-tolerant quantum computer. The tutorial is presented as three main sessions as below.

CryoModel: Cryogenic CMOS computer modeling tools

Cryogenic computing, which runs CMOS devices at extremely low temperatures is highly promising thanks to its significant reduction of wire resistance as well as leakage current.

In this session, we will introduce our modeling tools to accurately predict the performance and power consumption of various cryogenic CMOS computer devices. We will cover the modeling methodology, detailed tool usage, and use cases of our cryogenic DRAM, cache, and processor modeling tools. We will also present our cryogenic-optimized architectures which appeared in ISCA 2019, ASPLOS 2020, ISCA 2020, Top Picks 2021, ISCA 2021, and ASPLOS 2022.

Superconductor-based computer design and modeling tools

Superconductor single-flux quantum (SFQ) device operating at 4K or below enables at 4K, enables high-speed and low-power digital logical circuits. To exploit the SFQ device's full potential, we need to develop new architecture and circuit designs to exploit the new device characteristics (e.g., gate-level latching, limited fan-outs, and strict timing window).

In this session, we will introduce SFQ device, its features, our SFQ circuit/microprocessor designs, and area/power modeling which appeared in ISSCC 2019, VLSI 2020, MICRO 2020, Top Picks 2021, and ISCAS 2022.

XQsim: Fault-tolerant quantum control processor modeling tools

10+K qubit fault-tolerant quantum computer is essential to achieve a true sense of quantum supremacy. With the recent effort toward the large-scale quantum computer, architects have revealed various scalability issues in a quantum control processor. But, it has been difficult to identify and resolve the processor's scalability bottleneck due to the absence of a reliable tool. To resolve the challenge, we developed XQsim, an open-source cross-technology quantum control processor simulator.

In this session, we will introduce XQsim's detailed usage and capability based on our real use-case experiences. This session will explain our tools while covering microarchitecture, temperature, and technology exploration which appeared in ISCA 2022.

Agenda

Note

Please bring your laptop and install pre-required packages to fully enjoy our tool demonstrations!

sudo apt install python3.8-dev python3-pip libprotobuf-dev protobuf-compiler libboost-all-devpython3.8 -m pip install protobuf cython numpyOrganizers & Speakers

Related Publications

Our tutorial will be held in Chicago on Sunday, October 2, 2022, prior to the 55th IEEE/ACM International Symposium on Microarchitecture (MICRO).

Our tutorial will be held in Chicago on Sunday, October 2, 2022, prior to the 55th IEEE/ACM International Symposium on Microarchitecture (MICRO).